製品概要

アストロデザインでは、FPGAでJPEG XS のエンコード・デコードを行うIP (Intellectual Property) コアを開発し、製品化しました。

JPEG XSとは

映像は高精細になり、解像度・ビット深度・フレームレート・色域・輝度が拡大、それに伴いデータ量が増加し課題となっています。

●XS は“eXtra Small" & "eXtra Speed"

●ビジュアリロスレス(視覚的に損失が少ない)

●ローレイテンシー(エンコード・デコードの遅延が少ない)

JPEG XSはこのような問題を解決します

インターネットプロトコルを使用して高解像な画像を伝送したいが・・

▼高解像な画像は膨大なデータ量でネットワーク回線のトラフィックを圧迫

▼膨大なデータ量を安定して伝送できるシステムを構築すると全体の価格が高価

MPEG規格のエンコード/デコード(H.265/MPEG-H HEVC etc.)は圧縮効率は良いが・・

▼画質の劣化が大きい

▼レイテンシーが大きい

用途

●リモートライブビューイング

●SMPTE ST 2110システム

●バーチャルリアリティー(VR)

●デジタルシネマ

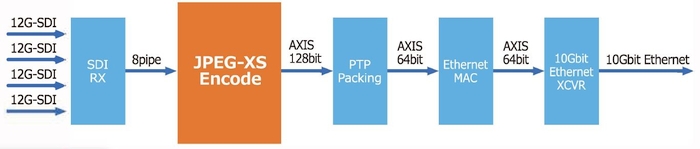

設計例

仕様

| プロファイル | Light 422.10、Light444.12 、Main422.10、Main444.12、High444.12 |

| 解像度 | 最大7680×4320 |

| フレームレート | 最大60p(4Kの場合120pが可能) |

| 色空間 | RGB、YCBCR |

| カラーサンプリング | 4:4:4、4:2:2、4:2:0 |

| ビット深度 | 8、10、12 、16bit |

| 圧縮率 | 1/3~1/36 |

| コードストリーム | CBR |

| インターフェース | AXIストリーム |

| 対応ベンダー | Xilinx、 Intel |

受託開発も行います

下記のような各種インターフェースを含め、JPEG XS FPGA IPコアを使用したモジュール基板や製品(カメラ、レコーダーなど)の開発受託を承ります。

・12G-SDI

・HDMI2.1

・DisplayPort

・SMPTE ST 2110

・10GbE/100GbE など